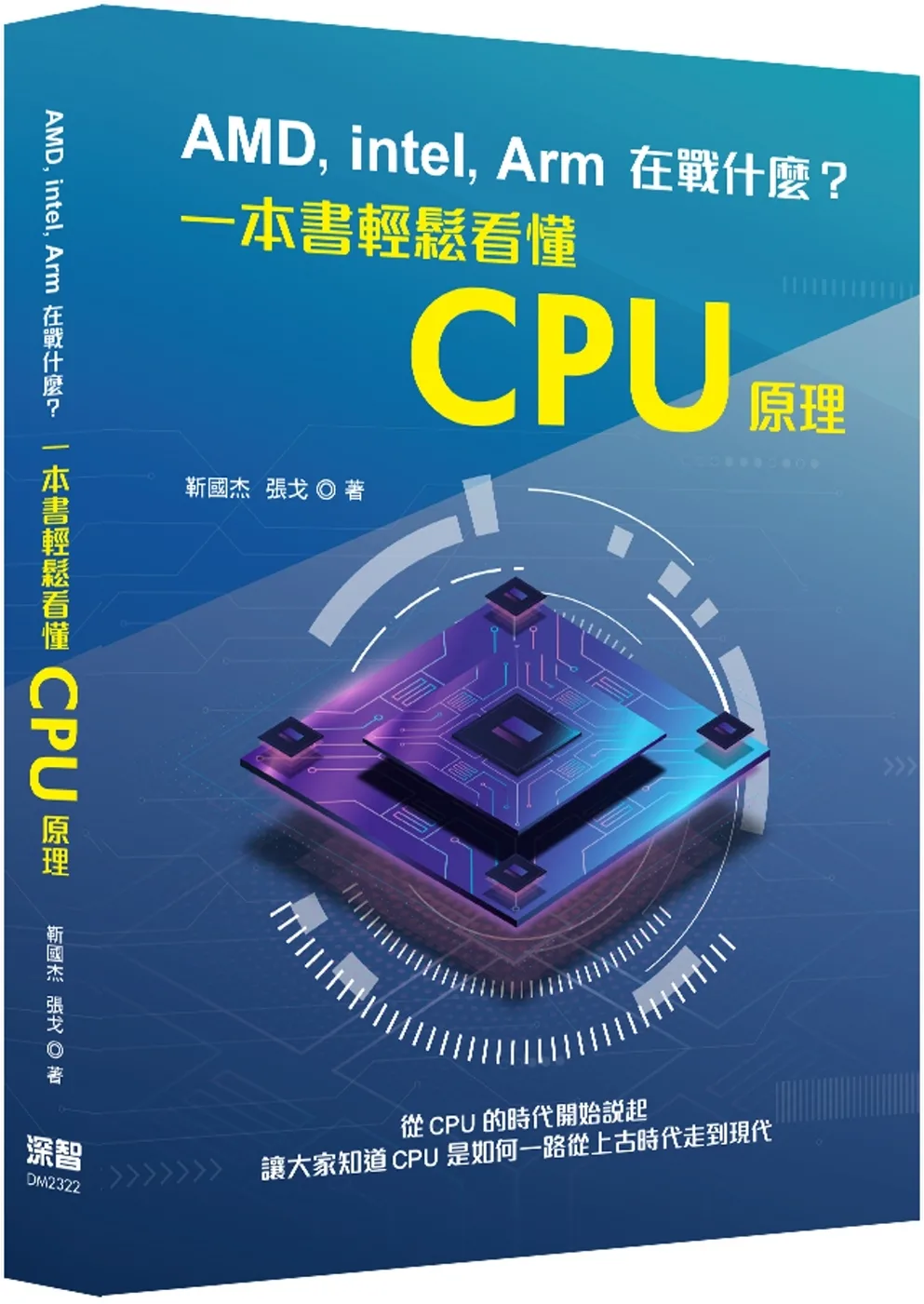

☆★☆ AIoT 時代三國鼎立,動手設計屬於自己的 CPU 開闢新時代,從本書開始!☆★☆

?

RISC-V是一個開放、開源的架構,人人都可獲取,因此,企業、學校和個人都可以主動參與相關的研發,這勢必能夠帶來更多的創新。

?

憑藉著簡潔、模組化且擴充性強的特點,RISC-V的晶片產品源源不絕地被推向市場,使得晶片產業得以蓬勃發展。這樣的發展趨勢終將推動RISC-V成為ISA領域的一項開放標準。每一次技術變遷都會帶來一個新生產業的崛起。從主機時代到PC時代,成就了Intel;從PC時代到行動時代,成就了ARM;從行動時代到AIoT時代,我們能否抓住RISC-V的機遇?

?

本書作者是著名RISC-V公司芯來科技的創辦人,曾在世界最大的半導體公司擔任高級工程師,也是華人地區少見專注於RISC-V的硬體公司。

?

本書以蜂鳥E203,為開發平台,這是中文地區最早被RISC-V基金會官方首?收錄的開放原始碼核心。在X86、ARM、之外,我們是否能靠著RISC-V再開闢出一條新的捷徑?看看Linux的成功,或許你已經參與了一個新時代的降臨。

?

【本書特點】

● CPU 的基礎知識、指令集架構的歷史。

● RISC-V 架構及其特點。

● 當前全世界的商業或開放原始碼 RISC-V 處理器。

● RISC-V 處理器核心的整體設計思想和頂層介面。

● RISC-V 處理器單選指單元、執行單元、交付單元微架構和原始程式。

● RISC-V 匯流排協定,以及該模組的微架構和原始程式、處理器的記憶體架構。

● RISC-V 的中斷和異常機制,硬體實現微架構和原始程式。

● RISC-V 架構定義的偵錯方案,硬體實現微架構和原始程式。

● RISC-V 的可擴充性,訂製一款輔助處理器。